Các interposer quang thế hệ tiếp theo sẽ kết nối nhiều chiplet với nhau với độ trễ thấp

Khi ngành công nghiệp chip chuyển sang lĩnh vực "multi-chiplet," nghiên cứu mới đã đưa ra một giải pháp thú vị cho kết nối chipset, sử dụng quang học silicon như các interposer quang.

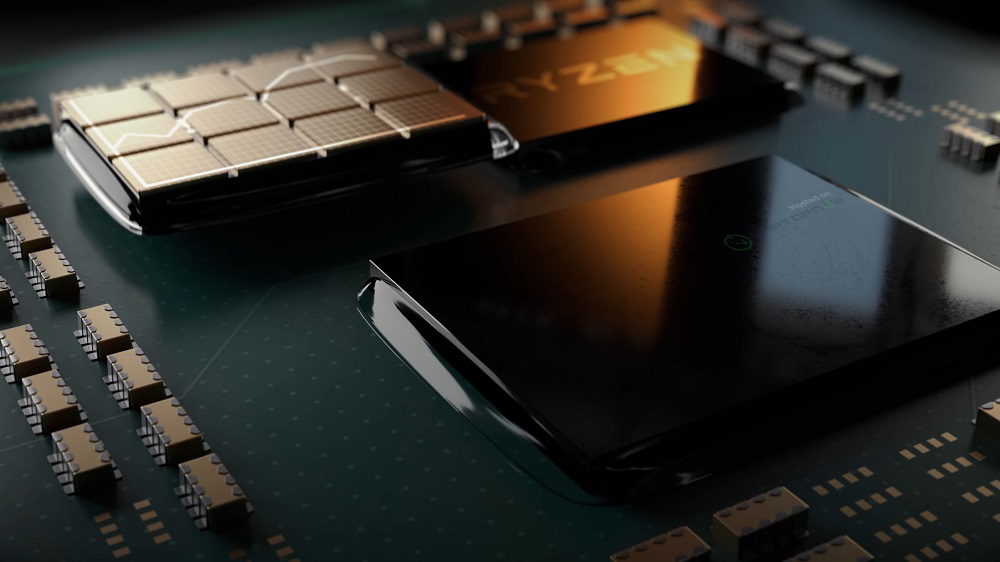

Cuộc đua thiết kế chiplet trong ngành CPU và GPU đang ngày càng nóng lên, đặc biệt là khi áp dụng kỹ thuật thiết kế cho các giải pháp tiết kiệm năng lượng.

Chiplet là sự kết hợp của nhiều chip khác nhau được tích hợp vào một gói duy nhất, với hệ thống kết nối giúp thúc đẩy ý tưởng về "thu nhỏ quy trình."

Bạn có thể có nhiều chiplet sử dụng cùng một IP lõi hoặc khác nhau, và các thiết kế có thể được kết hợp để mang lại hiệu suất tốt nhất cho một phân khúc sản phẩm. Tuy nhiên, điều quan trọng là phải có một phương pháp kết nối phù hợp.

Các phát hiện mới từ CEA-Leti, một viện nghiên cứu công nghệ châu Âu, cho thấy việc sử dụng interposer quang, dựa trên quang học silicon, có thể là một phương pháp hiệu quả cho kết nối chiplet và có khả năng giảm thiểu đáng kể độ trễ trong giao tiếp.

Cụ thể, các interposer quang này được gọi là Starac, và việc sử dụng quang học silicon với các kỹ thuật truyền thống khiến công nghệ này trở nên độc đáo và khả thi. Interposer quang chủ động Starac đã kết hợp mạch điện tử và quang học trong một gói, cho phép định tuyến và xử lý dữ liệu phức tạp. Ngoài ra, công nghệ này còn chứa một ONoC (Optical Network-on-Chip) dành riêng, chịu trách nhiệm truyền tải dữ liệu tốc độ cao giữa các chiplet mà không cần các bước trung gian thông qua cấu trúc topologi vòng.

Starac vẫn chưa được triển khai, vì vậy chúng ta không thể kết luận chắc chắn về các cải tiến hiệu suất mà nó sẽ mang lại. Tuy nhiên, CEA-Leti khẳng định rằng công nghệ này sẽ giảm độ trễ, cung cấp băng thông cao hơn và cải thiện hiệu suất năng lượng một cách đáng kể, cuối cùng thúc đẩy việc áp dụng bởi các nhà sản xuất chính.

Công ty đang hướng tới các đối tác trong ngành để đưa ý tưởng này vào thực tế, nhưng những phức tạp trong sản xuất cùng với chi phí cao liên quan đến kỹ thuật này đang cản trở họ.

./.

M.P theo Wccftech

Các interposer quang thế hệ tiếp theo sẽ kết nối nhiều chiplet với nhau với độ trễ thấp